Difference between revisions of "ZX Breakout"

| (8 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

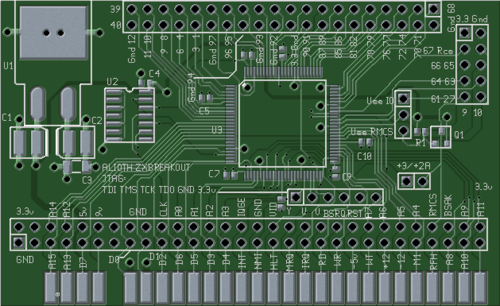

[[Image:Zxbreakout1.jpg|thumb|right|500px|ZX Breakout with XC95144XL]] | |||

This is a CPLD (complex programmable logic device) breakout board for the Spectrum (including 128K and Amstrad models). The original idea behind this board was to provide a breakout board for the ZX Spectrum bus signals, and also level shifting of all the signals to 3.3v with a second set of breakout pins. This was to provide an interface to chips that are not 5v tolerant, such as all current in-production FPGAs. | This is a CPLD (complex programmable logic device) breakout board for the Spectrum (including 128K and Amstrad models). The original idea behind this board was to provide a breakout board for the ZX Spectrum bus signals, and also level shifting of all the signals to 3.3v with a second set of breakout pins. This was to provide an interface to chips that are not 5v tolerant, such as all current in-production FPGAs. | ||

| Line 4: | Line 6: | ||

Either the Xilinx XC9572XL or the XC95144XL CPLD can be used on this board. To give a rough idea of the logic resources these CPLDs provide, Chris Smith's timing accurate ULA replacement fills an XC95144XL, that's to say this CPLD has a similiar amount of resource to the Spectrum ULA. | Either the Xilinx XC9572XL or the XC95144XL CPLD can be used on this board. To give a rough idea of the logic resources these CPLDs provide, Chris Smith's timing accurate ULA replacement fills an XC95144XL, that's to say this CPLD has a similiar amount of resource to the Spectrum ULA. | ||

=== Errata === | |||

Due to a dumb mistake, the ROMCS circuit is incorrect for the black +2 and +3 machines. If you intend to use the ZX Breakout with one of these, a simple workaround is to just not connect pin 4 of the edge connector (top side, 4th pin from the left) or desolder it if you've already connected it. The board will not work at all with a black +2 or +3 unless you do this, even if you're not planning to use ROMCS. It works fine with all other models as-is. | |||

== The board == | == The board == | ||

| Line 235: | Line 240: | ||

|- | |- | ||

|} | |} | ||

== Xilinx UCF file for pins == | |||

Copy and paste this into your UCF text constraints file for the list of pins. Comment out the signals you aren't using with a # in front of that line (ISE will fail at the fitter stage if you have nets defined in your UCF file which don't exist in your design). Signals with "_L" at the end are active low. Note that RESET is active high (it's been inverted). This is generally what you want; the Xilinx library components all have active high reset. The clock is also in phase with the Z80 clock. | |||

Also note that the pin used to control ROMCS can also be used as a GPIO, depending on the position of the jumper. ROMCS is active low from the point of view of the CPLD. | |||

This file will also appear in Subversion. | |||

GPIO pins are not listed in this file since you'll be defining them according to whatever function they may have. | |||

net A(0) loc=p32; | |||

net A(1) loc=p35; | |||

net A(2) loc=p37; | |||

net A(3) loc=p41; | |||

net A(4) loc=p59; | |||

net A(5) loc=p58; | |||

net A(6) loc=p56; | |||

net A(7) loc=p55; | |||

net A(8) loc=p40; | |||

net A(9) loc=p39; | |||

net A(10) loc=p36; | |||

net A(11) loc=p33; | |||

net A(12) loc=p15; | |||

net A(13) loc=p16; | |||

net A(14) loc=p13; | |||

net A(15) loc=p14; | |||

net D(0) loc=p18; | |||

net D(1) loc=p20; | |||

net D(2) loc=p22; | |||

net D(3) loc=p29; | |||

net D(4) loc=p30; | |||

net D(5) loc=p28; | |||

net D(6) loc=p25; | |||

net D(7) loc=p17; | |||

net MREQ_L loc=p50; | |||

net IORQ_L loc=p52; | |||

net RD_L loc=p53; | |||

net WR_L loc=p54; | |||

net M1_L loc=p60; | |||

net INT_L loc=p42; | |||

net NMI_L loc=p49; | |||

net CLK loc=p23; | |||

net RESET loc=p99; | |||

net ROMCS_L loc=p61; | |||

== Components used == | |||

{| class="wikitable" style="text-align: center; color: green;" | |||

! align="left"|Refdes | |||

! Component | |||

! Package | |||

! Mfr. | |||

! Description | |||

! Notes | |||

|- | |||

|U1||P565D2T33||D2PAK3||ON Semi||3.3v LDO regulator|| | |||

|- | |||

|U2||74HCT14||SOIC 14||Any||Schmitt trigger inverter, TTL compatible|| | |||

|- | |||

|U3||XC9572XL||TQFP 100||Xilinx||CPLD||Use XC95144XL for more logic resources | |||

|- | |||

|C1, C2||150uF||Tant B||Any||Capacitor|| | |||

|- | |||

|C3||1uF||1206||Any||Capacitor|| | |||

|- | |||

|C4 to C10||0.1uF||0603||Any||Capacitor|| | |||

|- | |||

|R1||300R||0603||Any||Resistor|| | |||

|- | |||

|Q1||BSS84P||SOT23||Infineon||P channel MOSFET|| | |||

|- | |||

|} | |||

ZX bus edge connector is an open ended 28 position 0.1 inch pitch connector, with position 5 contacts removed and replaced with a plastic key. This connector usually needs to be hand made by cutting down a larger connector (such as an old ISA bus connector). | |||

40 pin, 10 pin and 60 pin headers are up to the board's user. It's suggested that SIL sockets are used for the headers since this allows wires to be plugged in and connected to a breadboard etc. However, if a ribbon cable is to be used, a PCB to ribbon connector is recommended. | |||

It is suggested that normal jumper pin headers are used for the jumpers. | |||

== Projects for the ZX Breakout == | |||

* [[ZX SPI]] - An SPI interface for the Spectrum. | |||

[[Category:ZX Breakout]] | |||

Latest revision as of 15:06, 25 March 2019

This is a CPLD (complex programmable logic device) breakout board for the Spectrum (including 128K and Amstrad models). The original idea behind this board was to provide a breakout board for the ZX Spectrum bus signals, and also level shifting of all the signals to 3.3v with a second set of breakout pins. This was to provide an interface to chips that are not 5v tolerant, such as all current in-production FPGAs.

Using a CPLD instead of simple level shifters does two things: it provides the original functionality of a breakout board with a level shifter since a 3.3v CPLD with 5v tolerant IO can be used for this purpose, and for prototyping or making the logic for other things too - in other words, make a versatile breakout board for both the ZX bus and a CPLD.

Either the Xilinx XC9572XL or the XC95144XL CPLD can be used on this board. To give a rough idea of the logic resources these CPLDs provide, Chris Smith's timing accurate ULA replacement fills an XC95144XL, that's to say this CPLD has a similiar amount of resource to the Spectrum ULA.

Errata

Due to a dumb mistake, the ROMCS circuit is incorrect for the black +2 and +3 machines. If you intend to use the ZX Breakout with one of these, a simple workaround is to just not connect pin 4 of the edge connector (top side, 4th pin from the left) or desolder it if you've already connected it. The board will not work at all with a black +2 or +3 unless you do this, even if you're not planning to use ROMCS. It works fine with all other models as-is.

The board

The PCB features the following:

- All major ZX bus digital signals routed to the CPLD.

- Header for ZX signals, nearest the Spectrum edge connector.

- 3.3v linear power supply for the CPLD.

- JTAG header for programming the CPLD.

- Ability to control the ROMCS line.

- Clock is inverted (to be in phase with the CPU clock) by a Schmitt-trigger buffer giving sharper rising and falling edges.

- Two headers for CPLD signals - a 40 pin header with 32 CPLD general purpose IOs, and a 10 pin header with 7 general purpose IOs.

- 40 pin header laid out with ground and power pins in the same location as an IDE connector.

- 4 layer PCB with solid ground and power planes for ideal CPLD performance.

Additionally, the ZX signals and CPLD pin locations are shown in the silk screen, so you know what you're connecting to without having to reach for a datasheet.

Pin locations

ZX bus to CPLD

ZX bus function to CPLD function block mapping is optimized for the XC9572, being the smallest device with fewest resources. For the '72, the data bus and upper half of the address bus is grouped into function block 1, and the lower half of the address bus and control signals in function block 3. The remaining pins go to the GPIO headers.

The ZX clock is mapped to a global clock signal, and the reset signal is inverted and buffered and routed to the global system reset pin. A global clock signal is available on the GPIO header.

| ZX signal | CPLD pin | XC9572 FB | XC95144 FB | Comments |

|---|---|---|---|---|

| D0 | 18 | 1 | 1 | |

| D1 | 20 | 1 | 1 | |

| D2 | 22 | 1 | 1 | |

| D3 | 29 | 1 | 3 | |

| D4 | 30 | 1 | 3 | |

| D5 | 28 | 1 | 3 | |

| D6 | 25 | 1 | 3 | |

| D7 | 17 | 1 | 1 | |

| A0 | 32 | 3 | 3 | |

| A1 | 35 | 3 | 5 | |

| A2 | 37 | 3 | 5 | |

| A3 | 41 | 3 | 5 | |

| A4 | 59 | 3 | 7 | |

| A5 | 58 | 3 | 7 | |

| A6 | 56 | 3 | 7 | |

| A7 | 55 | 3 | 7 | |

| A8 | 40 | 1 | 5 | |

| A9 | 39 | 1 | 5 | |

| A10 | 36 | 1 | 5 | |

| A11 | 33 | 1 | 3 | |

| A12 | 15 | 1 | 1 | |

| A13 | 16 | 1 | 1 | |

| A14 | 13 | 1 | 1 | |

| A15 | 14 | 1 | 1 | |

| /MREQ | 50 | 3 | 7 | |

| /IORQ | 52 | 3 | 7 | |

| /RD | 53 | 3 | 7 | |

| /WR | 54 | 3 | 7 | |

| /M1 | 60 | 3 | 7 | |

| /INT | 42 | 3 | 5 | |

| /NMI | 49 | 3 | 5 | |

| CLK | 23 | 1 | 5 | Buffered; CPLD GCK2 |

| RESET | 99 | 2 | 3 | Buffered; CPLD GSR (active high) |

| ROMCS | 61 | 3 | 7 | Only when "Use ROMCS" is jumpered |

40 pin header

The 40 pin header is numbered using the ribbon cable style of numbering. Pin 1 is at the top right hand side of the connector, when looking down at the component side of the PCB, with the ZX edge connector at the bottom (in other words, as shown in the image on this page).

| Header pin | CPLD pin | XC9572 FB | XC95144 FB | Comments |

|---|---|---|---|---|

| 1 | 68 | 4 | 8 | |

| 2 | GND | |||

| 3 | 71 | 4 | 8 | |

| 4 | 70 | 4 | 8 | |

| 5 | 74 | 4 | 6 | |

| 6 | 72 | 4 | 8 | |

| 7 | 77 | 4 | 6 | |

| 8 | 76 | 4 | 6 | |

| 9 | 79 | 4 | 6 | |

| 10 | 78 | 4 | 6 | |

| 11 | 82 | 4 | 6 | |

| 12 | 81 | 4 | 6 | |

| 13 | 86 | 4 | 6 | |

| 14 | 85 | 4 | 6 | |

| 15 | 89 | 4 | 4 | |

| 16 | 87 | 2 | 4 | |

| 17 | 91 | 2 | 4 | |

| 18 | 90 | 4 | 4 | |

| 19 | GND | |||

| 20 | 3.3v | |||

| 21 | 92 | 2 | 4 | |

| 22 | GND | |||

| 23 | 93 | 2 | 4 | |

| 24 | GND | |||

| 25 | 94 | 2 | 4 | |

| 26 | GND | |||

| 27 | 95 | 2 | 4 | |

| 28 | 96 | 2 | 4 | |

| 29 | 97 | 2 | 4 | |

| 30 | GND | |||

| 31 | 1 | 2 | 2 | |

| 32 | 3 | 2 | 2 | GTS1 |

| 33 | 4 | 2 | 2 | GTS2 |

| 34 | 6 | 2 | 2 | |

| 35 | 8 | 2 | 2 | |

| 36 | 9 | 2 | 2 | |

| 37 | 10 | 2 | 2 | |

| 38 | 11 | 2 | 1 | |

| 39 | 12 | 2 | 1 | |

| 40 | GND |

10 pin header

This header uses ribbon cable numbering, with pin 1 being the top left pin looking down on the PCB, as in the image above.

Pin 4 is the same as the ROMCS pin on the header next to the edge connector - it's just a straight connection. It is provided as an alternative site to connect a wire to ROMCS. Pin 9 is not connected to the CPLD if the "Use ROMCS" jumper is closed. When this jumper is closed, CPLD pin 61 will go to the transistor controlling the ROMCS line allowing the CPLD to page out the ZX ROM. Pin 10 routes to a global clock pin, it may also be used as general purpose IO.

| Header pin | CPLD pin | XC9572 FB | XC95144 FB | Comments |

|---|---|---|---|---|

| 1 | 3.3v | |||

| 2 | GND | |||

| 3 | 67 | 4 | 8 | |

| 4 | ROMCS | |||

| 5 | 66 | 4 | 8 | |

| 6 | 65 | 4 | 8 | |

| 7 | 64 | 3 | 8 | |

| 8 | 63 | 3 | 8 | |

| 9 | 61 | 3 | 7 | May be routed to ROMCS |

| 10 | 27 | 1 | 3 | GCK3 |

Xilinx UCF file for pins

Copy and paste this into your UCF text constraints file for the list of pins. Comment out the signals you aren't using with a # in front of that line (ISE will fail at the fitter stage if you have nets defined in your UCF file which don't exist in your design). Signals with "_L" at the end are active low. Note that RESET is active high (it's been inverted). This is generally what you want; the Xilinx library components all have active high reset. The clock is also in phase with the Z80 clock.

Also note that the pin used to control ROMCS can also be used as a GPIO, depending on the position of the jumper. ROMCS is active low from the point of view of the CPLD.

This file will also appear in Subversion.

GPIO pins are not listed in this file since you'll be defining them according to whatever function they may have.

net A(0) loc=p32; net A(1) loc=p35; net A(2) loc=p37; net A(3) loc=p41; net A(4) loc=p59; net A(5) loc=p58; net A(6) loc=p56; net A(7) loc=p55; net A(8) loc=p40; net A(9) loc=p39; net A(10) loc=p36; net A(11) loc=p33; net A(12) loc=p15; net A(13) loc=p16; net A(14) loc=p13; net A(15) loc=p14; net D(0) loc=p18; net D(1) loc=p20; net D(2) loc=p22; net D(3) loc=p29; net D(4) loc=p30; net D(5) loc=p28; net D(6) loc=p25; net D(7) loc=p17; net MREQ_L loc=p50; net IORQ_L loc=p52; net RD_L loc=p53; net WR_L loc=p54; net M1_L loc=p60; net INT_L loc=p42; net NMI_L loc=p49; net CLK loc=p23; net RESET loc=p99; net ROMCS_L loc=p61;

Components used

| Refdes | Component | Package | Mfr. | Description | Notes |

|---|---|---|---|---|---|

| U1 | P565D2T33 | D2PAK3 | ON Semi | 3.3v LDO regulator | |

| U2 | 74HCT14 | SOIC 14 | Any | Schmitt trigger inverter, TTL compatible | |

| U3 | XC9572XL | TQFP 100 | Xilinx | CPLD | Use XC95144XL for more logic resources |

| C1, C2 | 150uF | Tant B | Any | Capacitor | |

| C3 | 1uF | 1206 | Any | Capacitor | |

| C4 to C10 | 0.1uF | 0603 | Any | Capacitor | |

| R1 | 300R | 0603 | Any | Resistor | |

| Q1 | BSS84P | SOT23 | Infineon | P channel MOSFET |

ZX bus edge connector is an open ended 28 position 0.1 inch pitch connector, with position 5 contacts removed and replaced with a plastic key. This connector usually needs to be hand made by cutting down a larger connector (such as an old ISA bus connector).

40 pin, 10 pin and 60 pin headers are up to the board's user. It's suggested that SIL sockets are used for the headers since this allows wires to be plugged in and connected to a breadboard etc. However, if a ribbon cable is to be used, a PCB to ribbon connector is recommended.

It is suggested that normal jumper pin headers are used for the jumpers.

Projects for the ZX Breakout

- ZX SPI - An SPI interface for the Spectrum.